EPCC实验室投递的论文"An Optimizing Framework on MLIR for Efficient FPGA-based Accelerator Generation"被体系结构领域顶级会议International Symposium on High-Performance Computer Architecture (HPCA 2024) 录用。今年HPCA收到410篇投稿,最终接受75篇,录用率18.3%。

距离正式会议交流和论文公布还有一段时间,我们在这里提前放出内容前瞻,对接受论文进行介绍。

论文标题:An Optimizing Framework on MLIR for Efficient FPGA-based Accelerator Generation

作者:Weichuang Zhang, Jieru Zhao, Guan Shen, Quan Chen, Chen Chen, Minyi Guo

工作简介:

FPGA作为一种可重构硬件,可以由用户自定义,来定制成高性能和低功耗的FPGA加速器。但是,传统的FPGA开发需要编写硬件描述语言,开发周期长、开发难度大、易错率高,影响了FPGA的大规模使用。现有高层次综合技术可以使工程师仅通过编写高层次综合代码来开发FPGA硬件,降低了编程门槛。然而,基于高层次综合代码的硬件实现往往难以达到高性能,需要经过一定时间的调试和代码修改,增加了开发成本。因此,如何既保证高性能,又缩短FPGA开发时间,成了一个新的挑战。

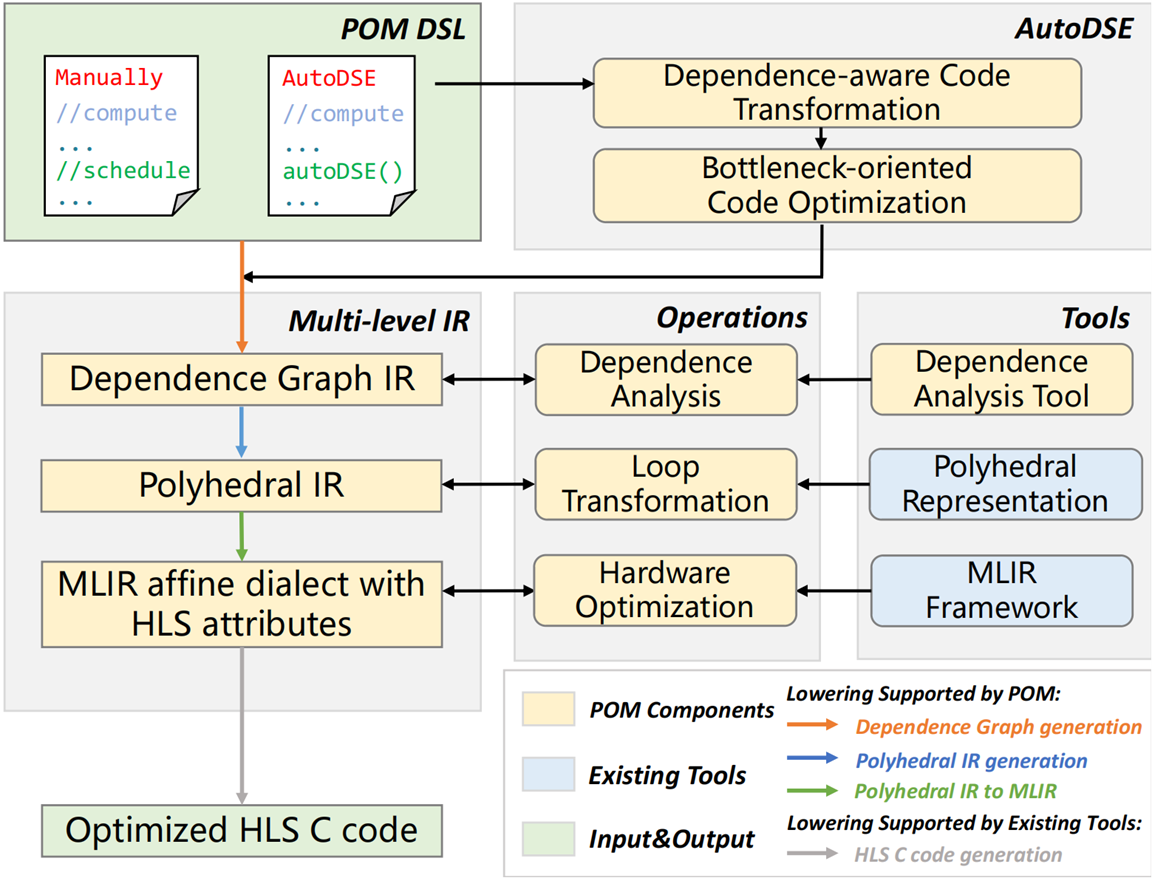

针对以上问题,我们提出了一套基于MLIR(multi-level intermediate representation)的编译框架——POM,用于自动生成高效的FPGA加速器。上图展示了POM编译框架的工作流程。POM提出了一套将算法与调度解耦的领域特定语言(domain-specific language, 即 DSL)作为输入,将抽象层级从 C/C++ 语言提高到DSL层级,降低了编程难度。编译框架前端进一步将算法和调度命令转换成多层中间表示。采用多层中间表示,可以使不同抽象层级的优化方法得以在合适的中间表示层上应用,有利于生成高性能的代码。在优化方面,POM引入了多面体模型来高效地支持多种循环优化的实现。最后,编译框架后端将多步优化后的中间表示转换成HLS 代码,输出给高层次综合工具综合成硬件 HDL 代码。

为了进一步提升生成代码的性能,POM提出了一套基于性能模型的高效自动搜索算法,通过参考估计的延迟等信息来寻找最佳或接近最佳的优化方案以追求最极致的性能。实现结果表明,与最新的SOTA(state-of-the-art)工作相比,POM在典型的benchmark上实现了平均6.46倍的加速比;在实际应用如EdgeDetect,VGG-16和ResNet-18上实现了平均6.06倍的加速比。